Introducción

El 80386 consiste en

una unidad central de proceso (CPU), una unidad de manejo de memoria (MMU) y

una unidad de interfaz con el bus (BIU).

La unidad de

instrucción decodifica los códigos de operación de las instrucciones que se encuentran

en una cola de instrucciones (cuya longitud es de 16 bytes) y los almacena en

la cola de instrucciones decodificadas (hay espacio para tres instrucciones).

La unidad de

segmentación provee cuatro niveles de protección para aislar y proteger

aplicaciones y el sistema operativo. Este tipo de protección por hardware

permite el diseño de sistemas con un alto grado de integridad.

El 80386 tiene dos

modos de operación: modo de direccionamiento real (modo real), y modo de direccionamiento

virtual protegido (modo protegido). En modo real el 80386 opera como un 8086

muy rápido, con extensiones de 32 bits si se desea. El modo real se requiere

primariamente para preparar el procesador para que opere en modo protegido. El

modo protegido provee el acceso al sofisticado manejo de memoria y paginado.

Dentro del modo

protegido, el software puede realizar un cambio de tarea para entrar en tareas

en modo 8086 virtual (V86 mode) (esto es nuevo con este microprocesador). Cada

una de estas tareas se comporta como si fuera un 8086 el que lo está

ejecutando, lo que permite ejecutar software de 8086 (un programa de aplicación

o un sistema operativo).

Diagrama en bloques del

80386

Versiones del 80386

_ 80386: En octubre

de 1985 la empresa Intel lanzó el microprocesador 80386 original de 16 MHz, con

una velocidad de ejecución de 6 millones de instrucciones por segundo y con

275.000 transistores. La primera empresa en realizar una computadora compatible

con IBM PC AT basada en el 80386 fue Compaq con su Compaq Deskpro 386 al año

siguiente.

_ 386SX: Para

facilitar la transición entre las computadoras de 16 bits basadas en el 80286,

apareció en junio de 1988 el 80386 SX con bus de datos de 16 bits y 24 bits de

direcciones (al igual que en el caso del 80286). Este microprocesador permitió

el armado de computadoras en forma económica que pudieran correr programas de

32 bits. El 80386 original se le cambió de nombre: 80386 DX.

_ 386SL: En 1990

Intel introdujo el miembro de alta integración de la familia 386: el 80386 SL

con varias características extras (25 MHz, frecuencia reducida ó 0 MHz,

interfaz para caché opcional externo de 16, 32 ó 64 KB, soporte de LIM 4.0

(memoria expandida) por hardware, generación y verificación de paridad, ancho

de bus de datos de 8 ó 16 bits) que lo hacen ideal para equipos portátiles.

Registros

del 80386

El 80386 tiene

registros de 32 bits en las siguientes categorías:

_ Registros de

propósito general.

_ Registros de

segmento.

_ Puntero de

instrucciones

_ Indicadores.

_ Registros de

control (nuevos en el 80386).

_ Registros de

direcciones de sistema.

_ Registros de

depuración (debug) (nuevos en el 80386).

_ Registros de test

(nuevos en el 80386).

Todos los registros

de los microprocesadores 8086, 80186 y 80286 son un subconjunto de los del

80386.

La siguiente figura

muestra los registros de la arquitectura base del 80386, que incluye los registros

de uso general, el puntero de instrucciones y el registro de indicadores. Los

contenidos de estos registros y de los selectores del párrafo siguiente son

específicos para cada tarea, así que se cargan automáticamente

al ocurrir una

operación de cambio de tarea. La arquitectura base también incluye seis

segmentos direccionables directamente, cada uno de 4 gigabytes de tamaño

máximo. Los segmentos se indican mediante valores de selectores puestos en los

registros de segmento del 80386. Si se desea se pueden cargar diferentes selectores

a medida que corre el programa.

Registros de propósito general

Los ocho registros de

propósito general de 32 bits mantienen datos y direcciones. Estos registros soportan

operandos de 1, 8, 16, 32 y 64 bits y campos de bits de 1 a 32 bits. Soportan

operandos de direcciones de 16 y de 32 bits. Los nombres simbólicos son: EAX, EBX,

ECX, EDX, ESI, EDI, EBP y ESP. Los 16 bits menos significativos se pueden

acceder separadamente. Esto se hace usando los nombres AX, BX, CX, DX, SI, DI, BP

y SP, que se utilizan de la misma manera que en los procesadores previos. Al

igual que en el 80286 y anteriores, AX se divide en AH y AL, BX se divide en BH

y BL, CX se divide en CH y CL y DX se divide en DH y DL.

Los ocho registros de

uso general de 32 bits se pueden usar para direccionamiento indirecto.

Cualquiera de los

ocho registros puede ser la base y cualquiera menos ESP puede ser el índice. El

índice se puede multiplicar por 1, 2, 4 u 8.

Ejemplos de

direccionamiento indirecto:

_ MOV ECX,[ESP]

_ MOV AL, [EAX + EDI

* 8]

_ ADD CL, [EDX + EDX

+ 8245525h]

_ INC DWORD PTR TABLA

[EAX * 4]

En modo real y en

modo 8086 virtual, la suma de la base, el índice y el desplazamiento debe estar

entre 0 y 65535 para que no se genere una excepción 13. El segmento por defecto

es SS si se utiliza EBP o ESP como base, en caso contrario es DS. En el caso de

usar direccionamiento de 16 bits, sólo se pueden usar las mismas combinaciones

que para el 8088. No se pueden mezclar registros de 16 y de 32 bits para direccionamiento

indirecto.

Registro de indicadores

Es un registro de 32

bits llamado EFlags. Los bits definidos y campos de bits controlan ciertas operaciones

e indican el estado del 80386. Los 16 bits menos significativos (bits 15-0)

llevan el nombre de Flags, que es más útil cuando se ejecuta código de 8086 y

80286. La descripción de los indicadores es la siguiente:

_ VM (Virtual 8086 Mode, bit 17): Este bit provee el modo

8086 virtual dentro del modo protegido.

Si se pone a 1 cuando

el 80386 está en modo protegido, entrará al modo 8086 virtual, manejando los

segmentos como lo hace el 8086, pero generando una excepción 13 (Violación

general de protección) en instrucciones privilegiadas (aquéllas que sólo se

pueden ejecutar en modo real o en el anillo

0). El bit VM sólo puede ponerse a 1 en modo protegido mediante la instrucción IRET.

_ OF (Overflow flag, bit 11): Si vale 1, hubo un desborde en

una operación aritmética con signo, esto es, un dígito significativo se perdió

debido a que tamaño del resultado es mayor que el tamaño del destino.

_ DF (Direction Flag, bit 10): Define si ESI y/o EDI se

autoincrementan (DF = 0) o

Autodecrementan (DF =

1) durante instrucciones de cadena.

_ IF (INTR enable Flag, bit 9): Si vale 1, permite el

reconocimiento de interrupciones externas señaladas en el pin INTR. Cuando vale

cero, las interrupciones externas señaladas en el pin INTR no se reconocen. IOPL

indica el máximo valor de CPL que permite la alteración del indicador IF cuando

se ponen nuevos valores en EFlags desde la pila.

_ TF (Trap enable Flag, bit 8): Controla la generación de la

excepción 1 cuando se ejecuta código paso a paso. Cuando TF = 1, el 80386

genera una excepción 1 después que se ejecuta la instrucción en curso.

_ ZF (Zero Flag, bit 6): Se pone a 1 si todos los bits del

resultado valen cero, en caso contrario se

pone a cero

.

_ AF (Auxiliary carry Flag, bit 4): Se usa para simplificar

la adición y sustracción de cantidades BCD empaquetados. AF se pone a 1 si hubo

un préstamo o acarreo del bit 3 al 4. De otra manera el indicador se pone a

cero.

_ PF (Parity Flag, bit 2): se pone a uno si los ocho bits

menos significativos del resultado tienen un número par de unos (paridad par),

y se pone a cero en caso de paridad impar (cantidad impar de unos). El

indicador PF es función de los ocho bits menos significativos del resultado, independientemente

del tamaño de las operaciones.

_ CF (Carry Flag, bit 0): Se pone a uno si hubo arrastre

(suma) o préstamo (resta) del bit más significativo del resultado.

Los bits 5 y 3 siempre valen

cero, mientras que el bit 1 siempre vale uno.

Registros de segmento del 80386

Son seis registros de

16 bits que mantienen valores de selectores de segmentos identificando los segmentos

que se pueden direccionar. En modo protegido, cada segmento puede tener entre

un byte y el espacio total de direccionamiento (4 gigabytes). En modo real, el

tamaño del segmento siempre es 64 KB.

Los seis segmentos

direccionables en cualquier momento se definen mediante los registros de

segmento CS, DS, ES, FS, GS, SS. El selector en CS indica el segmento de código

actual, el selector en SS indica el segmento de pila actual y los selectores en

los otros registros indican los segmentos actuales de datos.

Registros de control

El 80386 tiene tres

registros de control de 32 bits, llamados CR0, CR2 y CR3, para mantener el

estado de la máquina de naturaleza global (no el específico de una tarea

determinada). Estos registros, junto con los registros de direcciones del

sistema, mantienen el estado de la máquina que afecta a todas las tareas en el

sistema. Para acceder los registros de control, se utiliza la instrucción MOV.

Registros de direcciones del sistema

Cuatro registros

especiales se definen en el modelo de protección del 80286/80386 para referenciar

tablas o segmentos. Estos últimos son:

_ GDT (Tabla de

descriptores globales).

_ IDT (Tabla de

descriptores de interrupción).

_ LDT (Tabla de

descriptores locales).

_ TSS (Segmento de

estado de la tarea).

Las direcciones de

estas tablas y segmentos se almacenan en registros especiales, llamados GDTR, IDTR,

LDTR y TR respectivamente.

Registros de depuración

Al igual que en los

procesadores anteriores, el 80386 tiene algunas características que simplifica

el proceso de depuración de programas. Las dos características compartidas con

los microprocesadores anteriores son:

1) El código de

operación de punto de parada INT 3 (0CCh).

2) La capacidad de

ejecución paso a paso que provee el indicador TF.

Lo nuevo en el 80386

son los registros de depuración. Los seis registros de depuración de 32 bits accesibles

al programador, proveen soporte para depuración (debugging) por hardware. Los

registros DR0-DR3 especifican los cuatro puntos de parada (breakpoints). Como

los puntos de parada se indican mediante registros en el interior del chip, un

punto de parada de ejecución de instrucciones se puede ubicar en memoria ROM o

en código compartido por varias tareas, lo que no es posible utilizando el código

de operación INT 3. El registro de control DR7 se utiliza para poner y

habilitar los puntos de parada y el

registro de estado DR6 indica el estado actual de los puntos de parada. Después

del reset, los puntos de parada están deshabilitados. Los puntos de parada que

ocurren debido a los registros de depuración generan una excepción 1.

Registros de test

Se utilizan dos

registros para verificar el funcionamiento del RAM/CAM (Content Addressable Memory)

en el buffer de conversión por búsqueda (TLB) de la unidad de paginado del

80386. TR6 es el registro de comando del test, mientras que TR7 es el registro

de datos que contiene el dato proveniente del TLB. El TLB guarda las entradas

de tabla de página de uso más reciente en un caché que se incluye en el chip,

para reducir los accesos a las tablas de páginas basadas en RAM.

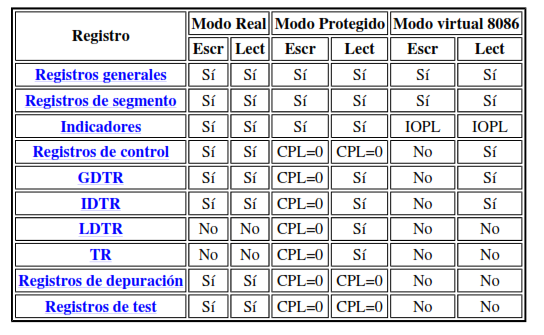

Acceso a registros

Hay algunas

diferencias en el acceso de registros en modo real y protegido, que se indican

a continuación.

Escr = Escritura del

registro, Lect = Lectura del

registro.

CPL=0: Los registros se pueden acceder sólo si el nivel de

privilegio actual es cero.

IOPL: Las instrucciones PUSHF y POPF son sensibles al

indicador IOPL en modo 8086 virtual.

Descriptores de segmento

Debido a la mayor

cantidad de funciones del 80386, estos descriptores tienen más campos que los descriptores

para el 80286.

El formato general de

un descriptor en el 80386 es:

_ Byte 0: Límite del

segmento (bits 7-0).

_ Byte 1: Límite del

segmento (bits 15-8).

_ Byte 2: Dirección base

del segmento (bits 7-0).

_ Byte 3: Dirección

base del segmento (bits 15-8).

_ Byte 4: Dirección

base del segmento (bits 23-16).

_ Byte 5: Derechos de

acceso del segmento.

_ Byte 6: Default

_ Byte 7:

Dirección base del segmento (bits 31-24).

Segmento de estado de la tarea

El descriptor TSS

apunta a un segmento que contiene el estado de la ejecución del 80386 mientras

que un descriptor de compuerta de tarea contiene un selector de TSS.

En el 80386 hay dos

tipos de TSS: tipo 286 y tipo 386. El primero es idéntico al TSS del microprocesador

80286, mientras que la del 80386 tiene el siguiente formato:

Nuevas instrucciones del 80386

Aparte de las instrucciones del 8088,

y las nuevas del 80186 y del 80286, el 80386 tiene las siguientes nuevas instrucciones:

BSF dest, src (Bit Scan Forward): Busca el primer bit puesto

a 1 del operando fuente src (comenzandopor el bit cero hasta el bit n-1). Si lo

encuentra pone el indicador ZF a 1 y carga el destino dest con el índice a

dicho bit. En caso contrario pone ZF a 0.

BSR dest, src (Bit Scan Reverse): Busca el primer bit puesto

a 1 del operando fuente src (comenzando por el bit n-1 hasta el bit cero). Si

lo encuentra pone el indicador ZF a 1 y carga el destino dest con el índice a

dicho bit. En caso contrario pone ZF a 0. BT dest, src (Bit Test): El bit del destino dest

indexado por el valor fuente se copia en el indicador CF.

BTC dest, src (Bit Test with Complement): El bit del destino dest

indexado por el valor fuente se copia en el indicador CF y luego se complementa

dicho bit.

BTR dest, src (Bit Test with Reset): El bit del destino dest

indexado por el valor fuente src se copia en el indicador CF y luego pone dicho

bit a cero.

BTS dest, src (Bit Test with Set): El bit del destino dest

indexado por el valor fuente src se copia en el indicador CF y luego pone dicho

bit a uno.

CDQ (Convert Doubleword to Quadword): Convierte el número

signado de 4 bytes en EAX en un número signado de 8 bytes en EDX:EAX copiando

el bit más significativo (de signo) de EAX en todos los bits de EDX.

CWDE (Convert Word to Extended Doubleword): Convierte una

palabra signada en el registro AX en una doble palabra signada en EAX copiando el

bit de signo (bit 15) de AX en los bits 31-16 de EAX.

JECXZ label (Jump on ECX Zero): Salta a la etiqueta label si

el registro ECX vale cero.

LFS, LGS, LSS dest, src (Load pointer using FS, GS, SS):

Carga un puntero de 32 bits de la memoria src al registro de uso general

destino dest y FS, GS o SS. El offset se ubica en el registro destino y el segmento

en FS, GS o SS. Para usar esta instrucción la palabra en la dirección indicada

por src debe contener el offset, y la palabra siguiente debe contener el segmento.

Esto simplifica la carga de punteros lejanos (far) de la pila y de la tabla de

vectores de interrupción.

MOVSX dest, src (Move with Sign eXtend): Copia el valor del

operando fuente src al registro destino dest (que tiene el doble de bits que el

operando fuente) extendiendo los bits del resultado con el bit de signo. Se

utiliza para aritmética signada (con números positivos y negativos).

MOVZX dest, src (Move with Zero eXtend): Copia el valor del

operando fuente src al registro destino dest (que tiene el doble de bits que el

operando fuente) extendiendo los bits del resultado con ceros. Se utiliza para

aritmética no signada (sin números negativos).

POPAD (Pop All Doubleword Registers): Retira los ocho registros

de uso general de 32 bits de la pila en el siguiente orden: EDI, ESI, EBP, ESP,

EBX, EDX, ECX, EAX. El valor de ESP retirado de la pila se descarta.

POPFD (Pop Doubleword Flags): Retira de la pila los indicadores

completos (32 bits).

No hay comentarios:

Publicar un comentario